- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

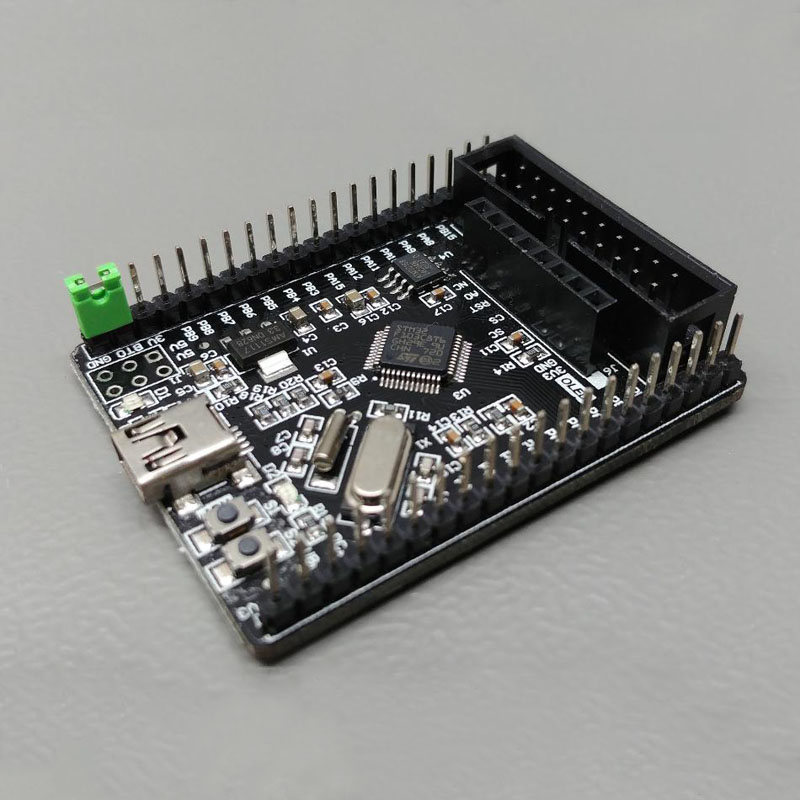

Płyta MCU ARM STM32

Ningbo Hi-tech Easy Choice Technology Co., Ltd jest firmą high-tech, która zajmuje się projektowaniem, rozwojem i produkcją płyty MCU ARM STM32. Reputacja naszej firmy opiera się na dobrych kredytach i świadczeniu wyjątkowych usług, co zaowocowało długoterminową współpracą ze znaczącymi korporacjami, agencjami rządowymi i szeroką społecznością użytkowników. Specjalizujemy się w opracowywaniu inteligentnych elektronicznych tablic kontrolnych, projektowaniu produktów do sterowania mechanicznego i elektrycznego, rozwój mikrokomputerów jednoukładowych, projektowanie obwodów i testy poprodukcyjne. Na zamówienie możemy zaprojektować obwód sterowania zgodnie z Twoimi potrzebami, umożliwiając realizację zamierzonych funkcjonalności produktu, niezależnie od tego, czy podasz wyraźne wymagania funkcjonalne, czy tylko pomysł.

Wyślij zapytanie

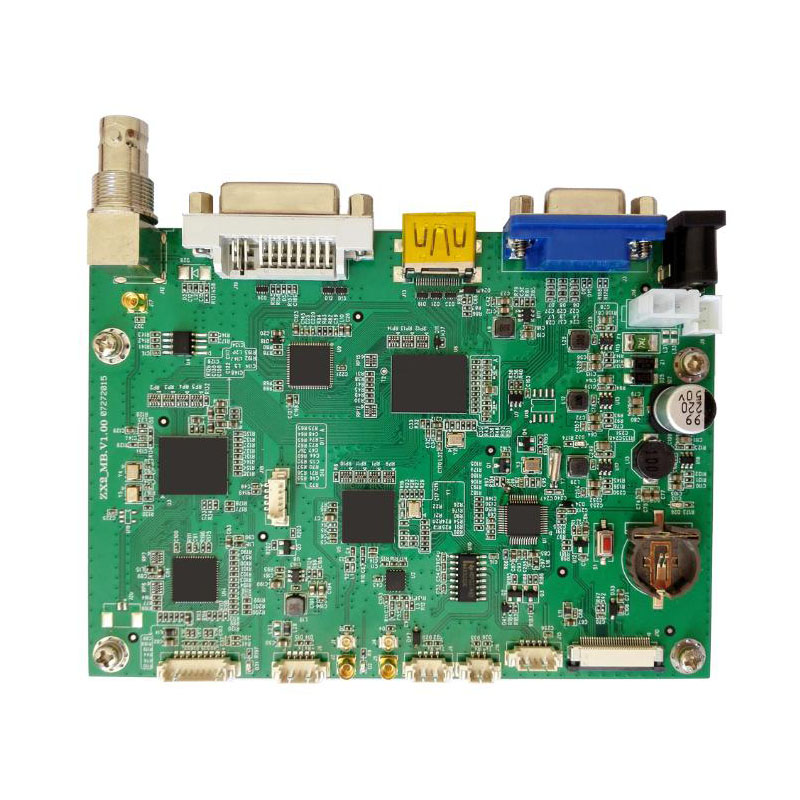

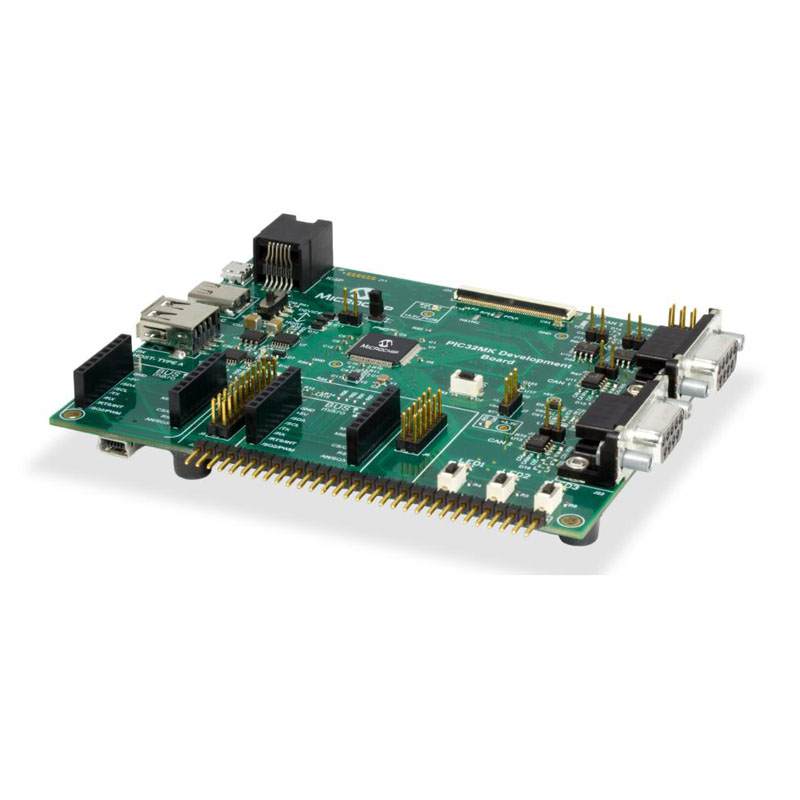

Rozwój płyt sterowania produktami przemysłowymi firmy YCTECH obejmuje projektowanie oprogramowania tablic sterowania przemysłowego, aktualizację oprogramowania, projektowanie schematów, projektowanie płytek drukowanych, produkcję płytek drukowanych i przetwarzanie PCBA na wschodnim wybrzeżu Chin. Nasza firma projektuje, rozwija i produkuje płytkę MCU ARM STM32. Rdzeń: procesor ARM32-bit Cortex-M3, najwyższa częstotliwość robocza to 72 MHz, 1,25 DMIPS/MHz. Mnożenie w jednym cyklu i dzielenie sprzętowe.

Pamięć: zintegrowana pamięć Flash o pojemności 32-512 KB. 6-64 KB pamięci SRAM.

Zegar, reset i zarządzanie energią: zasilanie 2,0-3,6 V i napięcie sterujące interfejsu I/O. Resetowanie po włączeniu zasilania (POR), resetowanie po wyłączeniu zasilania (PDR) i programowalny detektor napięcia (PVD). Oscylator kwarcowy 4-16MHz. Wbudowany obwód oscylatora RC 8MHz wyregulowany przed fabryką. Wewnętrzny obwód oscylatora RC 40 kHz. PLL dla zegara procesora. Kryształ 32kHz z kalibracją dla RTC.

Low power consumption: 3 low power consumption modes: sleep, stop, standby mode. VBAT to power the RTC and backup registers.

Tryb debugowania: debugowanie szeregowe (SWD) i interfejs JTAG.

DMA: 12-kanałowy kontroler DMA. Obsługiwane urządzenia peryferyjne: timery, ADC, DAC, SPI, IIC i UART.

Trzy 12-bitowe przetworniki A/D na poziomie amerykańskim (16 kanałów): Zakres pomiaru A/D: 0-3,6 V. Możliwość podwójnego próbkowania i wstrzymania. Czujnik temperatury jest zintegrowany na chipie.

2-kanałowy 12-bitowy przetwornik D/A: wyłącznie STM32F103xC, STM32F103xD, STM32F103xE.

Do 112 szybkich portów I/O: W zależności od modelu dostępnych jest 26, 37, 51, 80 i 112 portów I/O, z których wszystkie można mapować na 16 zewnętrznych wektorów przerwań. Wszystkie wejścia oprócz analogowych mogą przyjmować sygnały wejściowe do 5 V.

Do 11 timerów: 4 16-bitowe timery, każdy z 4 licznikami IC/OC/PWM lub licznikami impulsów. Dwa 16-bitowe 6-kanałowe zaawansowane timery sterujące: do wyjścia PWM można użyć do 6 kanałów. 2 timery watchdog (niezależny watchdog i watchdog okna). Timer Systick: 24-bitowy licznik w dół. Do sterowania przetwornikiem DAC używane są dwa 16-bitowe podstawowe zegary.

Do 13 interfejsów komunikacyjnych: 2 interfejsy IIC (SMBus/PMBus). 5 interfejsów USART (interfejs ISO7816, kompatybilny z LIN, IrDA, kontrola debugowania). 3 interfejsy SPI (18 Mbit/s), z których dwa są multipleksowane z IIS. Interfejs CAN (2.0B). Pełny interfejs USB 2.0. Interfejs SDIO.

Pakiet ECOPACK: mikrokontrolery serii STM32F103xx przyjmują pakiet ECOPACK.

efekt systemowy

1. Rdzeń ARM Cortex-M3 zintegrowany z wbudowaną pamięcią Flash i SRAM. W porównaniu z urządzeniami 8/16-bitowymi, 32-bitowy procesor RISC ARM Cortex-M3 zapewnia wyższą wydajność kodu. Mikrokontrolery STM32F103xx mają wbudowany rdzeń ARM, dzięki czemu są kompatybilne ze wszystkimi narzędziami i oprogramowaniem ARM.

2. Wbudowana pamięć Flash i pamięć RAM: Wbudowana do 512 KB wbudowanej pamięci Flash, która może być używana do przechowywania programów i danych. Do 64 KB wbudowanej pamięci SRAM można odczytywać i zapisywać z szybkością zegara procesora (bez stanów oczekiwania).

3. Zmienna pamięć statyczna (FSMC): FSMC jest wbudowane w STM32F103xC, STM32F103xD, STM32F103xE, z 4 wybieranymi chipami i obsługuje cztery tryby: Flash, RAM, PSRAM, NOR i NAND. 3 linie przerwań FSMC są podłączone do NVIC po OR. Nie ma FIFO odczytu/zapisu, z wyjątkiem PCCARD, kody są wykonywane z pamięci zewnętrznej, rozruch nie jest obsługiwany, a częstotliwość docelowa jest równa SYSCLK/2, więc gdy zegar systemowy wynosi 72 MHz, dostęp zewnętrzny jest wykonywany z częstotliwością 36 MHz.

4. Nested Vectored Interrupt Controller (NVIC): Może obsłużyć 43 maskowalne kanały przerwań (nie licząc 16 linii przerwań Cortex-M3), zapewniając 16 priorytetów przerwań. Ściśle sprzężony NVIC osiąga mniejsze opóźnienia przetwarzania przerwań, bezpośrednio przenosi adres tablicy wektorów wejściowych przerwań do jądra, ściśle sprzężony interfejs jądra NVIC, umożliwia wcześniejsze przetwarzanie przerwań, obsługuje przerwania o wyższym priorytecie, które pojawiają się później i obsługuje łańcuch końcowy, automatycznie zapisuje stan procesora, a wejście przerwania jest automatycznie przywracane po zakończeniu przerwania, bez interwencji instrukcji.

5. Zewnętrzny kontroler przerwań/zdarzeń (EXTI): Zewnętrzny kontroler przerwań/zdarzeń składa się z 19 linii detekcji krawędzi do generowania żądań przerwań/zdarzeń. Każda linia może być indywidualnie skonfigurowana, aby wybrać zdarzenie wyzwalające (zbocze narastające, zbocze opadające lub oba) i może być indywidualnie maskowana. Istnieje oczekujący rejestr do utrzymywania statusu żądań przerwań. EXTI jest w stanie wykryć, kiedy impuls na linii zewnętrznej jest dłuższy niż okres wewnętrznego zegara APB2. Do 16 zewnętrznych linii przerwań podłączonych jest do 112 GPIO.

6. Zegar i start: Nadal konieczne jest wybranie zegara systemowego podczas uruchamiania, ale wewnętrzny oscylator kwarcowy 8 MHz jest wybierany jako zegar procesora podczas resetowania. Można wybrać zewnętrzny zegar 4-16 MHz, który będzie monitorowany pod kątem powodzenia. W tym czasie sterownik jest wyłączony, a następnie wyłączone jest zarządzanie przerwaniami programowymi. Jednocześnie zarządzanie przerwaniami zegara PLL jest w pełni dostępne w razie potrzeby (np. w przypadku awarii pośrednio używanego oscylatora kwarcowego). Do konfiguracji częstotliwości AHB można użyć wielu komparatorów wstępnych, w tym szybkiego APB (PB2) i wolnego APB (APB1). Najwyższa częstotliwość szybkiego APB to 72 MHz, a najwyższa częstotliwość APB małej szybkości to 36 MHz.

7. Tryb rozruchu: Podczas uruchamiania pin rozruchu służy do wybrania jednej z trzech opcji rozruchu: import z pamięci flash użytkownika, import z pamięci systemowej i import z pamięci SRAM. Program do importu rozruchu znajduje się w pamięci systemowej i służy do przeprogramowania pamięci Flash przez USART1.

8. Schemat zasilania: VDD, zakres napięć wynosi 2,0 V-3,6 V, zewnętrzne zasilanie jest dostarczane przez pin VDD, który jest używany do we/wy i wewnętrznego regulatora napięcia. VSSA i VDDA, zakres napięć 2,0-3,6 V, zewnętrzne analogowe wejście napięciowe dla ADC, reset modułu, RC i PLL, w zakresie VDD (ADC jest ograniczony do 2,4 V), VSSA i VDDA muszą być odpowiednio podłączone do VSS i VDD. VBAT, zakres napięć 1,8-3,6 V, gdy VDD jest niepoprawny, zasila RTC, zewnętrzny oscylator kwarcowy 32KHz i rejestry zapasowe (realizowane przez przełączanie zasilania).

9. Power management: The device has a complete power-on reset (POR) and power-down reset (PDR) circuit. This circuit is always effective to ensure that some necessary operations are performed when starting from 2V or falling to 2V. When VDD is below a specific lower limit VPOR/PDR, the device can also remain in reset mode without an external reset circuit. The device features an embedded programmable voltage detector (PVD). The PVD is used to detect VDD and compare it to the VPVD limit. An interrupt is generated when VDD is lower than VPVD or VDD is greater than VPVD. The interrupt service routine can generate a warning message or place the MCU in a safe state. PVD is enabled by software.

10. Regulacja napięcia: Regulator napięcia posiada 3 tryby pracy: główny (MR), niski pobór mocy (LPR) oraz wyłączenie zasilania. MR jest używany w trybie regulacji (tryb pracy) w tradycyjnym sensie, LPR jest używany w trybie zatrzymania, a wyłączanie jest używane w trybie czuwania: wyjście regulatora napięcia ma wysoką impedancję, obwód rdzenia jest wyłączony, w tym zerowe zużycie (zawartość rejestrów i SRAM nie zostanie utracona).

11. Tryb niskiego zużycia energii: STM32F103xx obsługuje 3 tryby niskiego zużycia energii, aby osiągnąć najlepszą równowagę między niskim zużyciem energii, krótkim czasem uruchamiania i dostępnymi źródłami budzenia. Tryb uśpienia: tylko procesor przestaje działać, wszystkie urządzenia peryferyjne nadal działają, obudź procesor, gdy wystąpi przerwanie/zdarzenie; tryb zatrzymania: pozwala na zachowanie zawartości SRAM i rejestrów przy minimalnym zużyciu energii. Wszystkie zegary w obszarze 1,8 V są zatrzymane, oscylatory PLL, HSI i HSE RC są wyłączone, a regulator napięcia jest ustawiony w trybie normalnym lub niskim poborze mocy. Urządzenie można wybudzić z trybu zatrzymania za pomocą zewnętrznej linii przerwań. Zewnętrznym źródłem przerwań może być jedna z 16 zewnętrznych linii przerwań, wyjście PVD lub ostrzeżenie TRC. Tryb gotowości: W pogoni za najmniejszym zużyciem energii wewnętrzny regulator napięcia jest wyłączony, dzięki czemu obszar 1,8 V jest wyłączony. Oscylatory PLL, HSI i HSE RC są również wyłączone. Po przejściu w tryb czuwania, oprócz rejestrów zapasowych i obwodów czuwania, tracona jest również zawartość pamięci SRAM i rejestrów. Urządzenie wychodzi z trybu czuwania, gdy wystąpi reset zewnętrzny (pin NRST), reset IWDG, zbocze narastające na pin WKUP lub ostrzeżenie TRC. Po przejściu do trybu zatrzymania lub trybu czuwania, TRC, IWDG i powiązane źródła zegara nie zostaną zatrzymane.